Product Summary

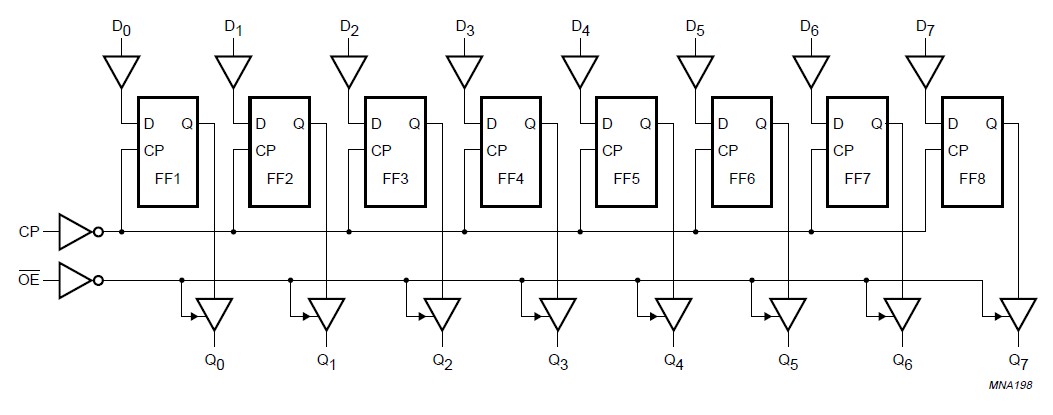

The 74AHC374PW is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL (LSTTL). It is specified in compliance with JEDEC standard No. 7A. The 74AHC374PW is an octal D-type flip-flop featuring separate D-type inputs for each flip-flop and 3-state outputs for bus oriented applications. A clock (CP) and an output enable (OE) input of the 74AHC374PW are common to all flip-flops. The 8 flip-flops will store the state of their individual D-inputs that meet the set-up and hold times requirements on the LOW-to-HIGH CP transition.

Parametrics

74AHC374PW absolute maximum ratings: (1)VCC DC supply voltage: -0.5 to +7.0 V; (2)VI input voltage range: -0.5 to +7.0 V; (3)IIK DC input diode current: -20 mA; (4)IOK DC output diode current: ±20 mA; (5)IO DC output source or sink current: ±25 mA; (6)ICC DC VCC or GND current: ±75 mA; (7)Tstg storage temperature range: -65 to +150 ℃; (8)PD power dissipation per package: 500 mW.

Features

74AHC374PW features: (1)ESD protection: HBM EIA/JESD22-A114-A exceeds 2000 V; MM EIA/JESD22-A115-A exceeds 200 V; CDM EIA/JESD22-C101 exceeds 1000 V; (2)Balanced propagation delays; (3)All inputs have Schmitt-trigger actions; (4)Inputs accepts voltages higher than VCC; (5)Common 3-state output enable input; (6)ICC category: MSI; (7)For AHC only: operates with CMOS input levels; (8)For AHCT only: operates with TTL input levels; (9)Specified from -40 to +85 and +125 ℃.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74AHC374PW |

NXP Semiconductors |

Flip Flops OCTAL D FLIP FLOP |

Data Sheet |

Negotiable |

|

||||||||||||

|

74AHC374PW,112 |

NXP Semiconductors |

Flip Flops OCTAL D FLIP FLOP |

Data Sheet |

|

|

||||||||||||

|

74AHC374PW,118 |

NXP Semiconductors |

Flip Flops OCTAL D FLIP FLOP |

Data Sheet |

|

|

||||||||||||

|

74AHC374PW-T |

NXP Semiconductors |

Flip Flops OCTAL D FLIP FLOP |

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))